基于FPGA的數字頻率計設計

Design digital cymometer of using FPGA

摘要:該數字頻率計的設計僅利用硬件描述語言來完成對系統功能的描述,在EDA工具的幫助下就可以得到最后的設計結果。所以盡管目標系統是硬件,但整個設計和修改過程如同完成軟件設計一樣方便和高效。

關鍵詞:數字頻率計;可編程邏輯器件;硬件描述語言。

Abstract:This project only utilizes Hardware Description Language to describe the function of system.With the help of EDA tool, we can get the final design.So although the target system is hardware,the whole design and modification is as efficient as software design.

Key words:digital cymometer,FPGA,VHDL

1. 引言

頻率計的基本功能是根據基準時鐘對被測時鐘進行檢測,并且被測時鐘的頻率值在數碼管顯示出來。這里采用的工作原理是利用基準時鐘產生1s的時間寬度,從而在這1s的時間寬度里對被測時鐘計數,然后將最后的計數結果送到數碼管顯示。

傳統的數字頻率計可以通過普通的硬件電路組合來實現,其開發過程、調試過程十分繁瑣,而且由于電子器件之間的互相干擾,影響頻率計的精度,也由于其體積較大,已不適應電子設計的發展要求。

采用EDA(Electronic Design Automation)的方法來完成頻率計的設計,即通過VHDL硬件描述語言的設計,用FPGA來實現。FPGA即現場可編程邏輯器件是由存放在片內RAM中的程序來設置其工作狀態的,因此,工作時需要對片內的RAM進行編程。用戶可根據不同的配置模式,采用不同的編程模式。加電時,FPGA芯片將EPROM中數據讀入片內編程RAM中,配置完成后,FPGA進入工作狀態。掉電后,FPGA恢復成白片,內部邏輯關系消失,因此,FPGA能夠反復使用。FPGA的編程無須專用的FPGA編程器,只需用通用的EPROM、PROM編程器即可。當需要修改FPGA功能時,只需換一片EPROM即可。這樣,同一片FPGA,不同的編程數據,可以產生不同的電路功能。因此,FPGA的使用非常靈活。同時EDA開發工具的通用性、設計語言的標準化以及設計過程幾乎與所用器件的硬件結構無關,所以設計成功的各類邏輯功能塊軟件有很好的兼容性和可移植性,可以在很短的時間里完成十分復雜的系統設計。

2. 設計實現

2.1. 邏輯結構描述

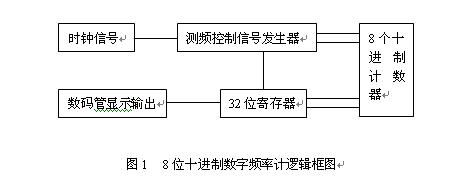

下圖1是8位十進制數字頻率計的邏輯框圖,它由一個測頻控制信號發生器、8個有時鐘功能的十進制計數器和一個32位鎖存器組成。

2.2. 硬件描述語言

測頻控制信號發生器:頻率測量的基本原理是計算每秒鐘內待測信號的脈沖個數。測頻控制信號發生器的計數使能信號tsten能產生一個1s脈寬的周期信號,并對頻率計的每一計數器的ENA使能端進行同步控制。當計數使能信號tsten為高電平時,允許計數;為低電平時停止計數,并保持其所計的脈沖數。在停止計數期間,首先需要一個鎖存信號load的上跳沿將計數器在前1s的計數值鎖存進32位鎖存器中,并由外部的7段譯碼器譯出和穩定顯示。設置鎖存器的好處是,顯示的數據穩定,不會由于周期性的清零信號而不斷閃爍。鎖存信號之后,必須有一清零clr_cnt對計數器進行清零,為下一秒的計數操作做準備。測頻控制信號發生器的工作時序如圖2所示。這個時序圖的產生首先建立了一個由D觸發器構成的二分頻器,在每次時鐘clk上沿到來時其值翻轉。

圖2 測頻控制信號發生器工作時序

其中控制信號時鐘clk的頻率取1Hz,那么信號tsten的脈寬恰好為1s,可以用作計數閘門信號。然后根據測頻的時序要求,可得出信號load和clr_cnt的邏輯描述。由圖2可見,在計數完成后,即計數使能信號tsten在1s的高電平后,利用其反相值的上跳沿產生一個鎖存信號load,0.5s后,clr_cnt產生一個清零信號上跳沿。高質量的測頻控制信號發生器的設計十分重要,可利用實時仿真可能產生的毛刺。

其VHDL邏輯描述如下:

Begin

Process(clk)

Begin

If clk’ event and clk = ‘1’ then

Div2clk <= not div2clk;

End if;

End process;

Begin

If clk = ‘0’ and div2clk = ‘0’ then clr_cnt <=’1’;

Else clr_cnt <=’0’;

End if;

End process;

Load <= not div2clk;

Tsten <=div2clk;

Ends behave;

寄存器:若已經有32位BCD碼存在于此模塊的輸入口,在信號load的上升沿后即被鎖存到寄存器的內部,并由寄存器的輸出端輸出,然后由實驗板上的7段譯碼器譯成能在數碼管上顯示輸出的相對應的數值。

該模塊的VHDL邏輯描述如下:

Begin

Process(clk)

Begin

If clk’ event and clk = ‘1’ then 1 Hz時鐘二分頻

Div2clk <= not div2clk;

End if;

End process;

Process(clk,div2clk)

Begin

If clk = ‘0’ and div2clk = ‘0’ then clr_cnt <= ‘1’;

產生計數器清零信號

Else clr_cnt <= ‘0’; tsten <=div2clk;

End behave;

計數器:如圖1所示,此十進制計數器的特殊之處是有一時鐘使能輸入端ENA,用于鎖定計數值。當高電平時計數允許,低電平時禁止計數。

計數器的VHDL邏輯描述為:

Begin

Process(clk,clr,ena)

Begin

If clr = ‘1’ then cqi <= 0;

Else if clk’ event and clk = ‘1’ then

If ena =’1’ then

If cqi < 9 then cqi <= cqi +1;

Else cqi <= 0; End ifl;

End if;

End if;

End process;

Process(cqi)

Begin

If cqi = 9 then carry_out <= ‘1’;

Else carry_out <= ‘0’;

End if;

End process;

Cq <= cqi;

End behave;

用測頻法設計的頻率計是在GW48-CK實驗箱上進行的模擬仿真,當輸入頻率為1Hz~750kHz的信號時,頻率計所測的頻率完全準確,當頻率高于750kHz時,出現誤差。因此該頻率計測頻范圍為1Hz~750kHz,在此測頻范圍內的測頻精度較高。

3. 結束語

用FPGA設計數字頻率計的方法大大減輕了電路圖設計和電路板設計的工作量和難度,減少了系統芯片的數量,縮小了系統的體積,提高了系統的可靠性。在設計過程中,可根據需要,隨時改變器件的內部邏輯功能和管腳的信號方式,具有很高的靈活性,避免了傳統設計方法中的再設計風險。另外,傳統設計方法的設計成果難以得到再利用,基于現代EDA技術的EPGA的設計成果經過修改、組合就能投入再利用,節省了開發成本并提高工作效率,是現代電子設計的上乘之選。

參考文獻:

[1] 冼進.Verilog HDL數字控制系統實例[M].中國水力水電出版社,2007年4月.

[2] 袁文波.FPGA應用開發從實踐到提高[M].中國電力出版社,2007年6月.

[3] 劉韜、樓興華.FPGA數字電子系統設計與開發實例導航[M].人民郵電出版社,2005年6月.

[4] 程云長.可編程邏輯器件與VHDL語言[M].科學出版社,2005年10月.

[5] 孟祥旭.FPGA應用開發從實踐到提高[M].中國電力出版社,2007年5月.

[6] http://www.100lw.com/article/2007/1005/article_15218.html

[7] http://www.eefocus.com/html/08-05/4322404030513AwLd_1.shtml